# Implementation of a Novel Pwm Dc-Dc Converter

# A.E.Anyalebechi

(Nnamdi Azikiwe University Awka, Anambra State, Nigeria.

**Abstract:** This paper presents the implementation of a soft-switching boost dc-dc converter. Passive soft-switching is employed due to its advantages over the active soft-switching and its ability to reduce switching losses. A Laplace transform-based analysis of the converter circuit was carried out to obtain design information which was already published. A complete circuit of the soft switching PWM dc-dc converter prototype is also presented here. Experimental results obtained from the prototype agree closely with the predicted results and this demonstrates the feasibility of the system.

Keywords: dc-dc converter, soft switching, pulse width modulation, boost converter, Laplace transform.

Date of Submission: 14-05-2018

Date of acceptance: 30-05-2018

·

#### I. Introduction

This paper is a follow-up to an already published paper: "A NOVEL SOFT SWITCHING PWM DC-DC CONVERTER". In the published paper a Laplace transform-based analysis of the dc-dc converter was carried out to obtain design information. Here the design information is taken some steps further to derive the values of different parameters in a typical soft switching pulse width modulated DC-DC converter.

Semiconductor device switching at high frequency is a major contributor to power loss in converters. Switching devices absorb power when they turn on or off if they go through a transition when both voltage and current are non-zero. As the switching frequency increases, these transitions occur more often and the power loss in the device increases. High switching frequencies are otherwise desirable because of the reduced size of filter components and transformers which reduce the size and weight of the converter circuits.

In resonant switching circuits, switching takes place when the switching device voltage and/or current are/is zero, thus avoiding simultaneous transitions of voltage and current and thereby eliminating switching losses. This type of switching is called "soft" switching. Resonant converters include resonant switch-mode converters, load resonant converters, and resonant de link converters [1].

A successful soft-switching scheme should be able to reduce the switching losses, diode reverse recovery losses, and switching voltage and current stresses on converter components. Any of the two main soft switching approaches which include the zero-current switching and the zero-voltage switching may be employed depending on the semiconductor device

technology that will be used. For example, MOSFETs present better performance under zero-voltage

switching (ZVS). This is because under zero-current switching the capacitive turn-on losses increase the switching losses and the electromagnetic interference (EMI). On the other hand, insulated gate bipolar transistor (IGBTs) and bipolar junction transistors (BJTs) present better results under zero- current switching (ZCS) which can avoid the turn-off losses caused by the tail current [2].

Furthermore, the last twenty years have witnessed an intensive research with the sole aim of achieving lossless switching of semiconductor devices. Lossless

switching increases circuit efficiency and makes high frequency operation possible thereby reducing the size and weight of circuit components. Several dc-dc converter configurations aimed at achieving a percentage degree of this goal have been proposed [3,4,5,6,7,8,9]. Each of these proposed circuit topologies has at least one of the following limitations:

- (a) Too many circuit components, thus degrading circuit reliability,

- (b) High current/voltage stresses on the circuit components,

- (c) Complex control circuitry which may include switching current/voltage level detection circuits,

- (d) Parasitic capacitor turn-on loss of some of the circuit switches,

- (e) Limitation of the output voltage control range to allow for switching transients.

In this paper, a detailed study of the single stage dc-dc employing a versatile and efficient soft-switching circuit cell is presented. In the presented converter, the turn-off and the turn-on of the main active switch and the corresponding freewheeling diode take place under zero-current and/or zero-voltage switching. Also, the turn-on and the turn-off of the circuit cell semiconductor devices take place under zero-current and/or zero-voltage switching. A lossless switching is achieved under the above scheme while the voltage and current

stresses are drastically reduced to the barest minimum through clamping techniques. Figure 1 shows a schematic block diagram of a conventional dc-dc converter.

#### II. Active/Passive Soft Switching

Higher switching frequencies allow reduction of the magnetic component sizes with pulse width modulated (PWM) switching converters. Unfortunately, increased switching frequencies cause higher switching losses and greater electro-magnetic interference (EMI). The switching loss mechanisms include the current and voltage overlap loss during the switching interval and the capacitance loss during turn-on. The diode reverse recovery also causes an additional conduction loss and further contributes to the current and voltage overlap loss. Soft switched pulse width modulated converters can either be passively soft switched or actively soft switched. Active or passive soft-switching methods have been used to reduce these switching losses.

Recently, passive soft switching has received renewed inspection as a better alternative to active methods. Passive methods do not require an extra switch or additional control circuitry. They are less expensive, have higher reliability and have been reported to achieve higher performance/price ratios than active methods [10, 11]. For PWM converters, passive soft switching reduces switching losses by lowering the active switch's di/dt and dv/dt to achieve zero-current turn-on and zero-voltage turn off. Furthermore, by controlling the di/dt of the active switch, the reverse recovery currents of the diodes are also controlled. The only loss mechanism not recovered with the passive techniques is the energy in the internal capacitance of the switch. However, this loss is much smaller than the other switching losses and may be smaller than the loss incurred by using an auxiliary switch in an active method [10, 11]. Historically, passive soft switching techniques were used to reduce spikes in the switching circuits and were lossy by dissipating the recovered switching energy in resistors [12]. But more recently, many lossless and partially lossless techniques have been proposed [10, 13].

The two necessary components that must be added to the circuit to achieve passive zero-current turn on and zero-voltage turn off are a small inductor and a capacitor. The inductor provides zero-current turn on of the active switch and limits the recovery current of the diodes while the capacitor provides zero-voltage turn off of the active switch. However, the topological rules that describe where these components must be placed in the circuit have not been proposed in the literature. Typically the inductor and capacitor have been placed in series and parallel respectively with the active switch. But many other locations are possible and can lower the component count and reduce switch stress. Also additional circuitry accompanying the capacitor and inductor is used to recover their energy to either the load or the input. There are many different proposed circuits to accomplish this. Furthermore, circuitry cells can be constructed that simplify the creation of new soft switching circuits.

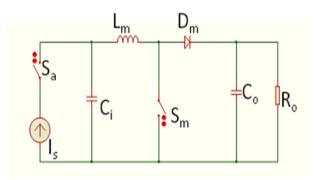

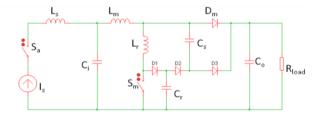

$S_a$  = auxiliary switch;  $I_s$  = supply current;  $C_i$  = input capacitor;  $C_o$  = output capacitor;  $S_m$  = main switch;  $R_o$  = output resistor(load);  $L_m$  and  $D_m$  are the main inductor and diode respectively. Figure 1: The Hard switched boost converter

#### **III. Continuous Current Mode**

A series connection of the stray inductance and d.c. source voltage is equivalent to a constant current source. Hence, the continuous current mode analysis is as shown below. The circuit has a switching period of T. from figure (1), immediately the main active switch is closed the inductor current rises from an initial value of  $I_{L1}$  to a final value of  $I_{L2}$  the average of which gives the average input current. When the switch turns off at the end of the on period, the energy stored in the inductor is transferred to the load.

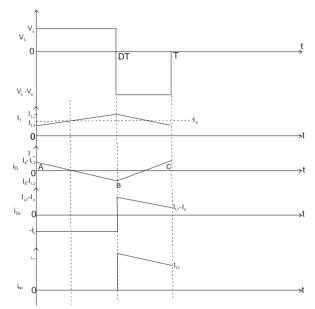

The switching waveforms, shown in figure (2), indicate that the output capacitor conducts a positive current only during off period.

DOI: 10.9790/1676-1303020108 www.iosrjournals.org 2 | Page

Figure 2: Continuous current switching waveforms

Using average voltage across inductor,

$$\frac{1}{T}[V_sDT + (V_s - V_o)(1 - D)T] = 0$$

$$V_sD + V_s(1-D) - V_o(1 - D) = 0$$

$$V_s-V_o(1-D) = 0$$

$$\frac{Vo}{Vs} = \frac{1}{1-D}$$

......

From equation (1), the variation of the duty cycle D gives different values of output voltage with a value tending to infinity as D tends to 1. Also, the average inductor current  $(I_s)$  can be the mean of the maximum and minimum value as follows:

We can also determine the average of  $i_{ci}$  and  $i_{co}$  from the switching waveforms  $I_{ci}$  = average of  $i_{ci}$  = area of (A + B + C)

$$\begin{split} &= \frac{1}{T} [1/2 (I_s - I_{L1}) \frac{DT}{2} + 1/2 (I_{s-} I_{L2}) \left\{ \frac{(1+D)T}{2} - \frac{DT}{2} \right\} \\ &\quad + 1/2 (I_s - I_{L1}) \{ \frac{(1-D)T}{2} \} \end{split}$$

Ici should be zero over one complete cycle.

That is

$$I_{ci} = 0 = \frac{\frac{1}{2}(I_s - I_{L1})\left(\frac{DT}{2} + \frac{(1-D)T}{2}\right) + \frac{1}{2}(I_s - I_{L2})(\frac{T}{2})}{T}$$

$$= \frac{\frac{1}{2}(I_s - I_{L1})\frac{T}{2} + \frac{1}{2}(I_s - I_{L2})\frac{T}{2}}{T}$$

Simplifying further we have,

$$\begin{split} &I_{S} - I_{L1} + I_{S} - I_{L2} = 0 \\ &I_{S} = \frac{1}{2} [I_{L1} + I_{L2}] \end{split}$$

Similarly, for the average of ico, which should be zero also, we have;

$$\begin{split} I_{co} &= \frac{1}{T} [-I_o DT + \int_0^{(1-D)T} (I_{L2} - I_0 - \frac{(I_{L2} - I_{L1})}{(1-D)T} t dt)] = 0 \\ &= -I_o D + [(I_{L2} - I_0)t - \frac{(I_{L2} - I_{L1})}{2(1-D)T} t^2]_0^{(1-D)T} \\ &= -I_o D + (I_{L2} - I_o)(1-D) - \frac{(I_{L2} - I_{L1})}{2} (1-D) \\ 0 &= -I_o D + \frac{(I_{L2} + I_{L1})}{2} (1-D) - I_0 + I_o D \end{split}$$

Therefore,

$$I_0 = \frac{(I_{L2} + I_{L1})}{2} (1 - D)$$

$$\frac{I_0}{I_s} = (1 - D)$$

-----4

Equation (4) is another way of deriving equation (3).

Note

$$I_S = \frac{1}{2} (I_{L2} + I_{L1})$$

.

But

$$V_S = (1 - D)V_0$$

$$\therefore \Delta I_L = \frac{[(1 - D)V_0 - V_0](1 - D)T}{L}$$

$$= -D \frac{(1 - D)V_0 T}{L}$$

$$= -D \frac{(1 - D)V_0}{fL}$$

$$= -D \frac{(1-D)V_0}{L}$$

$$= -D \frac{(1-D)V_0}{fL}$$

Again maximum  $\Delta I_L$  occurs at D =  $\frac{1}{2}$

Hence in magnitude,

$$\Delta I_{L_{max}} = \frac{V_0}{4fL}$$

Hence,

$$\frac{\Delta I_{Lmax}}{2} = \frac{V_0}{8fL} - - - - - - 8$$

From the above equation (8) the maximum and minimum inductor currents then become

$$I_{L1} = I_s - \frac{V_s D}{2fL} = I_s - \frac{D(1-D)V_0}{2fL} - --9$$

$$I_{L2} = I_s + \frac{V_s D}{2fL} = I_s + \frac{D(1-D)V_0}{2fL} - --10$$

For continuous current mode

$$I_{L1} = \; I_8 - \frac{V_8 D}{2 f L} = \; I_8 - \frac{D(1-D) V_0}{2 f L} \geq 0 \; ---11$$

otherwise current is discontinuous for  $I_{L1} < 0$ .

The critical inductance for continuous load

$$\begin{aligned} & \text{current for given D, V}_s \text{ and I}_s \text{ is,} \\ & \text{Lc} = \frac{V_S \text{ D}}{2 \text{fls}} = \frac{D (1 - D) V_o}{2 \text{fls}} \end{aligned}$$

By power balance the input power is equal to the output power, hence

$$V_S I_S = \frac{V_O^2}{R} = I_O V_O$$

That is,  $I_S = \frac{V_O^2}{RV_S} = \frac{I_O V_O}{V_S}$

Also,  $Is = \frac{I_0}{I - D}$  as was derived before.

The minimum inductance that will guarantee continuous current (the critical inductance), Lc can therefore be expressed in several forms as:

$$\begin{split} L_C &= \frac{V_S D (1-D)}{2 f I_0} = \frac{D (1-D)^2 V_0}{2 f I_0} \\ &= \frac{D (1-D)^2 R_0}{2 f} - - - - - 12 \end{split}$$

In terms of the output quantities note that equations (9), (10), (11) can be stated as,

$$I_{L1} = \frac{I_o}{1-D} - \frac{D(1-D)V_o}{2fL} \dots \dots 13$$

$$I_{L2} = \frac{I_o}{1-D} + \frac{D(1-D)V_o}{2fL} \dots \dots 14$$

Otherwise the current is discontinuous

# IV. The Input And Output Capacitors' Voltage Ripples

The peak to peak ripple on C<sub>o</sub> can be calculated from the fact that C<sub>o</sub> discharges at constant current in the interval

$$\Delta V_{C_O} = \frac{I_O}{C_O} DT = \frac{V_O}{C_O R} DT$$

This peak to peak ripple in per unit of the output voltage is,  $\frac{\Delta V_{Co}}{V_o} = \frac{D}{fRC_o} \dots \dots \dots 16$

$$\frac{\Delta V_{Co}}{V_o} = \frac{D}{fRC_o} \dots \dots \dots 16$$

Also the voltage on the input capacitor can be calculated from the input capacitor current waveform of fig (2) as

$$\begin{split} \Delta V_{C_1} &= \frac{\text{area } (A+C) \text{of } i_{c_1}}{c_i} = \frac{\text{area B of } i_{c_1}}{c_i} \\ &= \frac{1/2 \big( I_S - I_{L_1} \big) DT/2 \, + \frac{\big( I_S - I_{L_2} \big) (1-D)T/2}{2}}{C_i} \\ &= \frac{\frac{1/_2 (\, I_S - I_{L_1} \,)^{\, T}/_2}{C_i}}{\text{Ci}} \\ \text{But } I_S - I_{L1} &= \frac{V_S \, D}{2 \text{fL}} \\ & \therefore \Delta V_{C_1} = \frac{V_S \, DT}{2 \text{fLC}_i} \, \text{x} \, \frac{1}{4} = \frac{V_S D}{8 \text{f}^2 \text{LC}_i} \end{split}$$

The peak ripple voltage on the input capacitor is therefore

$$\frac{\Delta v_{c_1}}{2} = \frac{v_s D}{16f^2 L c_i} - - - - - 17$$

In per unit of the supply voltage the peak ripple voltage can be expressed as  $\frac{\Delta V_{C_i}}{V_S} = \frac{D}{8f^2LC_i} - - - - 18$

$$\frac{\Delta V_{C_i}}{V_S} = \frac{D}{8f^2LC_i} - - - - 18$$

Our target is to design a circuit which can give an output voltage of 230 volts from a supply voltage of 48 volts over a load of about 105.8 ohms. Hence the average continuous load current can be calculated as,  $I_0 = \frac{v_0}{R_0} = \frac{230}{105.8} = 2.174A$

$$I_0 = \frac{V_0}{R_0} = \frac{230}{105.8} = 2.174A$$

Also, recall that from our initial analysis [equation (1)] the transfer function for a continuous current circuit is,

$$V_0 = \frac{V_s}{1-D}$$

Therefore for a supply voltage of 48 volts and output voltage of 230 volts we have,

$$V_0 = \frac{V_s}{1-D}$$

$$230 = \frac{48}{1-D}$$

$$230 - 230D = 48$$

$$\therefore D = \frac{230-48}{230} = 0.79$$

From the above calculations, our desired circuit will operate at a duty cycle of about 0.79

Considering equation (12) the critical inductance which is the minimum inductance that will guarantee a continuous current operation is given by

$$L_{C} = \frac{D(1-D)^{2}R_{0}}{2f} = \frac{0.79(1-0.79)^{2}x105.8}{2x20000} = 92.15 \ \mu H$$

Also, assuming an output voltage ripple of less than one percent the output capacitor can be calculated from equation (16) as,

$$\frac{\Delta V_{C_0}}{V_0} = \frac{D}{fRC_0} < 1\%$$

$$\therefore C_0 > \frac{D}{Rf(\frac{\Delta V_{C_0}}{V_0})} = \frac{0.79}{105.9x200000x0.01}$$

$$\therefore C_0 > 37.3 \mu F$$

$C_0 \approx 40 \mu F$

Likewise from equation (18) for a ripple voltage of less than 1% under continuous current mode we can calculate the input capacitor as,

$$\begin{split} &C_{i} > \frac{D}{8f^{2}L(\frac{\Delta V_{C_{i}}}{V_{s}})} \\ &C_{i} > \frac{0.79}{8x(20000)^{2} \times 0.000095 \times 0.01} \\ &C_{i} > 260\mu F \end{split}$$

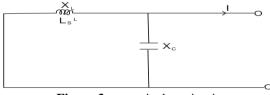

When the d.c source is connected in series with an inductance, it has an equivalence of a constant current source. The a.c equivalence can be drawn as follows,

Figure 3: ac equivalent circuit

$$\frac{\Delta I_L}{2} = \frac{V_0}{8fL} = I$$

The peak current flowing through the stray inductance is expected to be less than 1%

$$\frac{-jX_c}{j(X_L - X_C)} x I < 0.01$$

Considering the magnitude,

$$\frac{X_c}{X_L - X_c} \le 0.01$$

$$\therefore 100 X_C = X_L - X_c$$

$$101X_c = X_L$$

But  $X_c = \frac{1}{2nfC_i}$

Assuming

$$C_i = 100 \mu F$$

$$X_L = 2\pi f L_s$$

$$\frac{101}{2\pi x 20000 x 100 x 10^{-6}} = 2\pi x 20000 L_S$$

$$8.037 = 125663.7 L_S$$

$$\therefore L_S = \frac{8.037}{125663.7} = 64 \mu H$$

The stray inductance can be arbitrarily chosen to be 100μH.

The design of the soft-switching converter proceeds as follows: immediately auxiliary switch  $S_a$  in figure (1) is closed the current flow is the same as that shown in figure below, giving an output current of;

$$I_0 = \frac{P_0}{V_0} = \frac{500}{230} = 2.174A$$

Figure 4: circuit operation after closing Sa

Let  $L_m=200\mu H$  for continuous load current. The supply current can be calculated from equation (4) as,  $I_8=\frac{2.174}{1-0.79}=10.35 A$

$$I_8 = \frac{2.1/4}{1-0.79} = 10.35A$$

This is average value of  $i_{Lm}$ . The peak to peak current variation is:

$$\Delta I_{L} = \frac{V_{S}D}{2fL} = \frac{48 \times 0.79}{2 \times 20000 \times 200 \times 10^{-6}}$$

$$= \frac{48 \times 0.79}{8}$$

$$= 4.74 \text{ A}$$

$$I_{L_1} = 10.35 - 4.74 = 5.61 \text{ A}$$

$I_{L_2} = 10.35 + 4.74 = 15.09 \text{ A}$

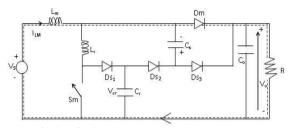

Figure 5: Soft switching dc-dc converter circuit model

## V. Conclusion

The compl The soft switching dc-dc pulse width modulation converter designed and implemented is as shown in figure 5 above. The parameter values are as gotten using Laplace-transformed design expressions. The circuit was implemented and was used to light a 230 volts rated bulb.

## References

- [1]. B. T. Lin, K.W. Siu and Y. S. Lee, "Actively clamped zero current switched Quasi Resonant Converters Using IGBT", IEEE Trans. On Industrial Electronics, Vol. 46 No.1 pp.75-81, Feb. 1999.

- [2]. Daniel W. Hart, "Introduction to Power Electronics", Prentice Hall, New Jersey (07458), 1999.

- R. Rangan et al, "Application of Insulated gate bipolar transistor to zero-current switching converters", IEEE Trans. Power [3]. electronics, vol. 4, pp. 2-7, Jan. 1989. C. A. Canesin, C.M.C. Duarte, and I.Barbi, "A new family of pulse-width-modulated zero-current –switching dc/dc converters", in

- [4]. IEEJ IPEC Rec., 1995, pp. 1379-1384.

- G. Hua and F.C Lee, "Soft-switching techniques in PWM converters", in Int. Conf. Ind. Electron., Control and Instrumentation, [5]. 1993, pp. 637-643.

- [6]. A. Elasser and D. A Torrey, "Soft-switching active snubbers for dc/dc converters", IEEE Trans. Power Electron., vol. 11, pp. 710-722, Sept. 1996.

- I. Husain and M. Ehsani, "Analysis of high Power soft-switching dc-dc converters using basic three-terminal structures", in Int. [7]. Conf. Ind. Electron., Control and Instrumentation, 1995, pp. 252-257.

- R. L. Steigerwald, "A review of soft-switching techniques in high performance dc power supplies", in IECON, 1995, PP. 1-7.

- R. L Steigerwald, R. W. De Donker, and M. H Kheraluwala, "A comparison of high-power dc-dc soft-switched converter [9]. topologies", IEEE Trans. Ind Applicat., vol. 32 pp. 1139-1145, Sept./Oct.1996.

- [10]. Helio Leaes Hey, Carlos Marcelo de Oliveira Steing, "A true ZCZVT Commutation cell for PWM Converters", IEEE Trans. Power

- Electron Vol. 15, No. 1, January 2000.

Julian Y. Zhu, Daohong Ding, "Zero-voltage- and zero-current-switched PWM DC-DC Converters using Active sunbber", IEEE Trans. On Industr. Applic. Vol. 35. No. 6 Nov/Dec. 1999. [11].

- T. A Meynard and H. Foch, "Multilevel conversion: High-voltage choppers and voltage-source inverters", in proc PESC' 92 Conf. [12]. Rec., 1992, pp. 397-403

- Eduardo Deschamps & Ivo Barbi, "A Flying-capacitor ZVS PWM 1.5KW DC-DC Converter with half of the input voltage across [13]. the switches", IEEE Trans. on Pow. Electron. Vol. 15, No. 5, Sept. 2000.

A.E.Anyalebechi "Implementation of a Novel Pwm Dc-Dc Converter "IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) 13.3 (2018): 01-08.

DOI: 10.9790/1676-1303020108 8 | Page www.iosrjournals.org